SystemCSP a graphical language for designing concurrent component-based embedded control systems

Graduation committee:

prof.dr. H. Brinksma, prof. dr. ir. M. Aksit, prof.dr. H. Corporaal, prof. dr. A. van Deursen, prof.dr. ir. J. van Amerongen, dr.ir. J.F. Broenink

Control Eengineering, Centre for Telematics and Information Technology (CTIT), Faculty of Electrical Engineering, Mathematics and Computer Science, University of Twente

CTIT PhD thesis series, ISSN: 1381-3617 CTIT number: TR-CTIT-07-55

This research was financially supported by the PROGRESS program of STW, the Dutch Technology Foundation

#### ISBN: 978-90-365-2573-2

Cover design by Bojan Orlic

Copyright © 2007 by B. Orlic

No part of this work may be reproduced by print, photocopy, or any means without permission of the author.

Printed by PrintPartners Ipskamp, Enschede, The Netherlands

## SYSTEMCSP

#### A GRAPHICAL LANGUAGE FOR DESIGNING CONCURRENT COMPONENT-BASED EMBEDDED CONTROL SYSTEMS

#### DISSERTATION

to obtain the doctor's degree at University of Twente, on the authority of the rector magnificus, prof. dr. W.H.M. Zijm, on account of the decision of the graduation committee to be publicly defended on Thursday, 20<sup>th</sup> September 2007 at 16.45h

by

Bojan Orlić

born on 11<sup>th</sup> February, 1976. in Bor, Serbia This dissertation is approved by: prof.dr.ir. Job van Amerongen, the promotor dr.ir. Jan F. Broenink, the assistant promotor

#### TABLE OF CONTENTS

| ACKNOW | VLEDGMENT                               | XI   |

|--------|-----------------------------------------|------|

| SUMMAR | Y                                       | XIII |

| 1 INTI | RODUCTION                               | 1    |

| 1.1    | CONTROL SYSTEMS APPLICATION AREA        | 2    |

| 1.2    | SOFTWARE DEVELOPMENT PRACTICE           | 5    |

| 1.2.1  | Structured approaches                   | 5    |

| Vi     | sual programming.                       | 6    |

|        | ormal verification                      |      |

|        | oncurrency                              |      |

| 1.3    | SYSTEMCSP APPROACH                      |      |

| 1.3.1  | - · · · · · · · · · · · · · · · · · · · |      |

| 1.3.2  |                                         |      |

| 1.3.3  | Brief overview of SystemCSP             | 11   |

| 1.4    | OUTLINE OF THE THESIS                   | 13   |

| 2 BAC  | KGROUND                                 | 15   |

| 2.1    | CSP AND ITS IMPLEMENTATIONS             |      |

| 2.1    |                                         |      |

| 2.1.1  |                                         |      |

| 2.1.2  | 1 0                                     |      |

|        |                                         |      |

| 2.1.4  | 1                                       |      |

| 2.1.5  |                                         |      |

|        | xternal (deterministic) Choice          |      |

|        | onditional (IF) choice<br>ternal choice |      |

| 2.1.6  |                                         |      |

| 2.1.0  | 8                                       |      |

|        |                                         |      |

| 2.1.8  |                                         |      |

| 2.1.9  |                                         |      |

| 2.2    | VISUALIZING CONCURRENT SYSTEMS          |      |

| 2.2.1  |                                         |      |

|        | itique                                  |      |

| 2.2.2  |                                         |      |

| 2.2.3  |                                         |      |

|        | quential                                |      |

|        | rallel                                  |      |

|        | noice                                   |      |

|        | ecursion                                |      |

|        | epresenting FSM-like designs            |      |

|        | iorities                                |      |

|        | aceptions                               |      |

|        | esign process                           |      |

|        | ata-flow orientation                    |      |

| 2.2.4  | Discussion                              | 41   |

| 2.3    | COMPONENT ENGINEERING PRACTICE          |      |

|        |                                         |      |

|   | 2.3.1      | Component frameworks                                            |      |

|---|------------|-----------------------------------------------------------------|------|

|   | 2.3.2      | Interaction management – the notion of contracts and connectors | 45   |

|   | 2.3.3      | Discussion                                                      | .47  |

|   | 2.4        | CONCLUSIONS                                                     | .48  |

| 3 | SYST       | TEMCSP                                                          | .49  |

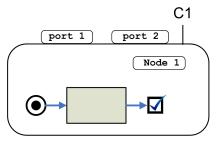

|   | 3.1        | BASIC ELEMENTS                                                  | .50  |

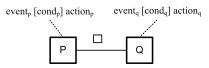

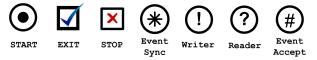

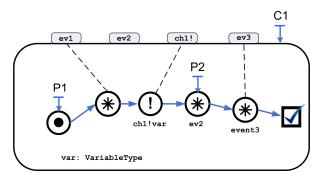

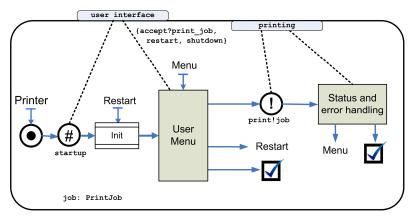

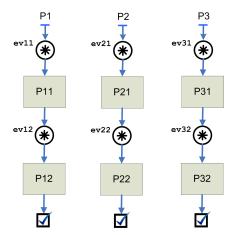

|   | 3.1.1      | Events                                                          | 50   |

|   | Ev         | ent-ends                                                        | 50   |

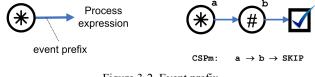

|   | Ev         | ent prefix                                                      |      |

|   | 3.1.2      |                                                                 |      |

|   |            | pcess labels                                                    |      |

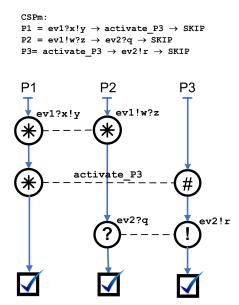

|   |            | eracting processes                                              |      |

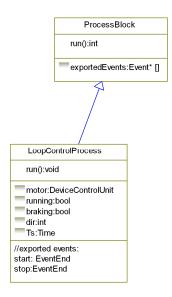

|   |            | ocess blockson-interacting process blocks                       |      |

|   | 3.1.3      |                                                                 |      |

|   | 3.2<br>3.2 | Comments                                                        |      |

|   |            |                                                                 |      |

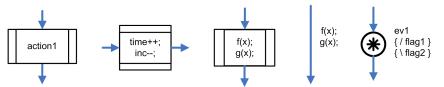

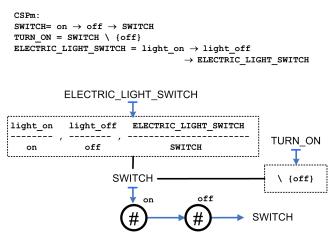

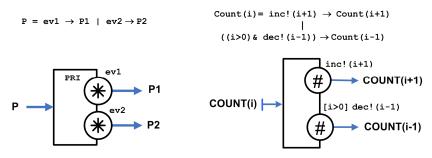

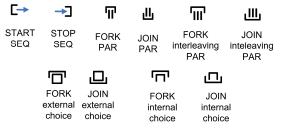

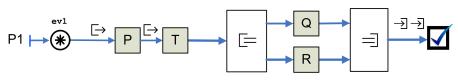

|   | 3.2.1      | Elements related to CSP operators                               |      |

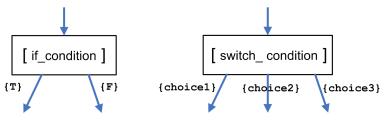

|   |            | nditional choice                                                |      |

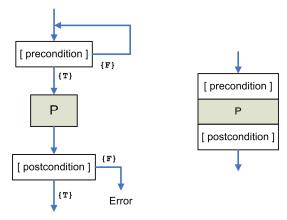

|   |            | econditions and postconditions                                  |      |

|   |            | arded alternative                                               |      |

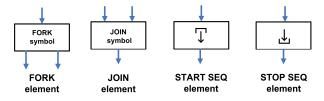

|   |            | art and Exit Control Flow Elements                              |      |

|   | Sp         | ecifying synchronization alphabet                               | . 60 |

|   | Ex         | ception Handling                                                |      |

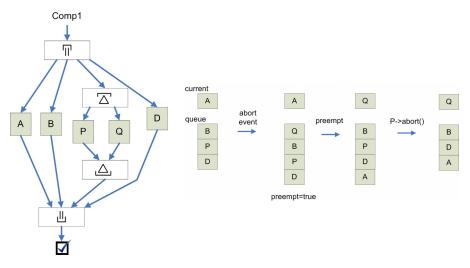

|   | 3.2.2      | Supervision elements                                            | 63   |

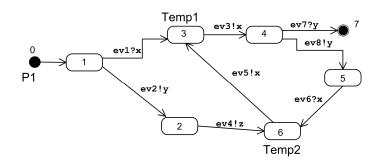

|   | 3.2.3      | FSM-like diagrams in SystemCSP                                  | .64  |

|   | 3.2.4      | Hiding as a filter of possible interactions                     | .64  |

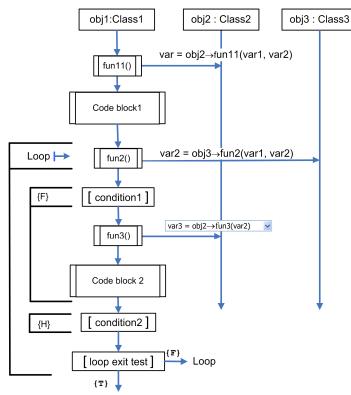

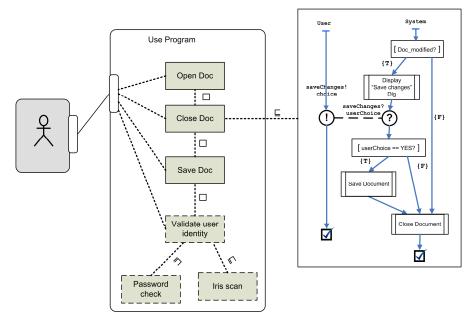

|   | 3.2.5      | SystemCSP sequence diagrams                                     | .66  |

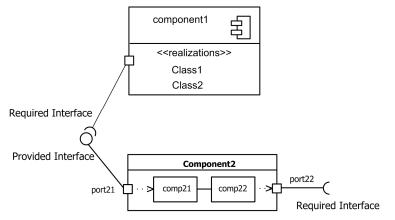

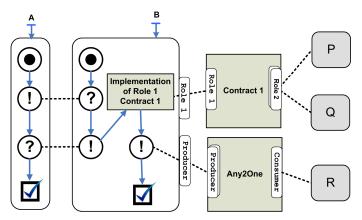

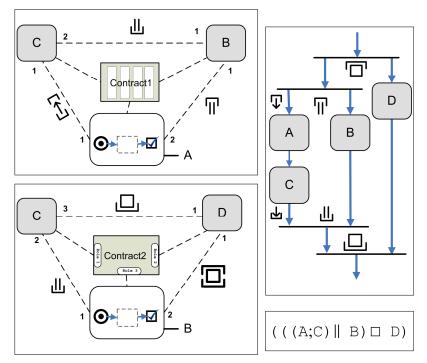

|   | 3.3        | INTERACTION ORIENTED ELEMENTS                                   | .68  |

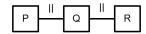

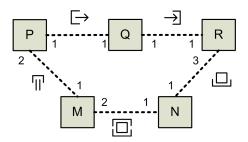

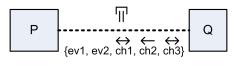

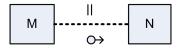

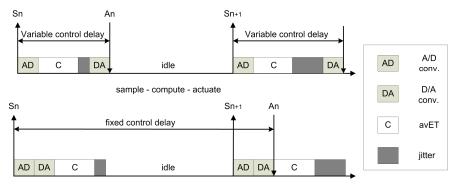

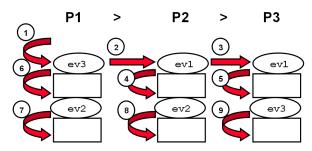

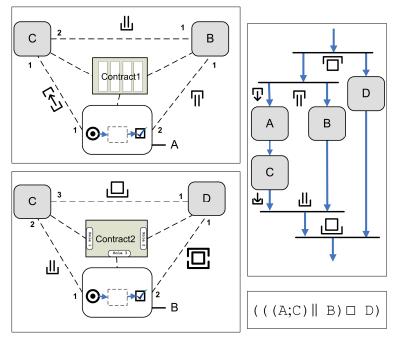

|   | 3.3.1      | Binary compositional relationships                              | . 68 |

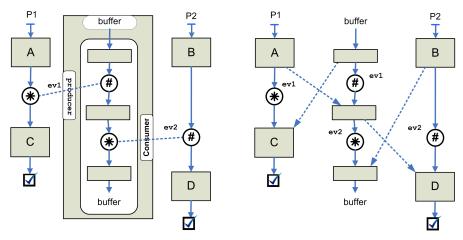

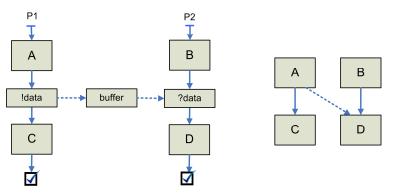

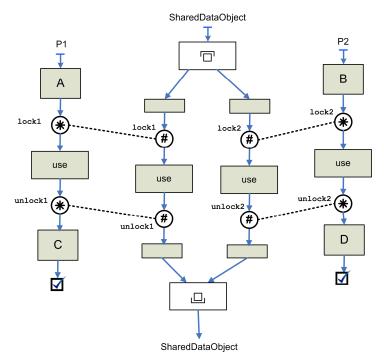

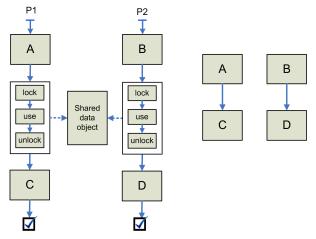

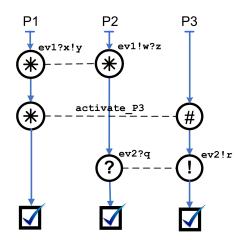

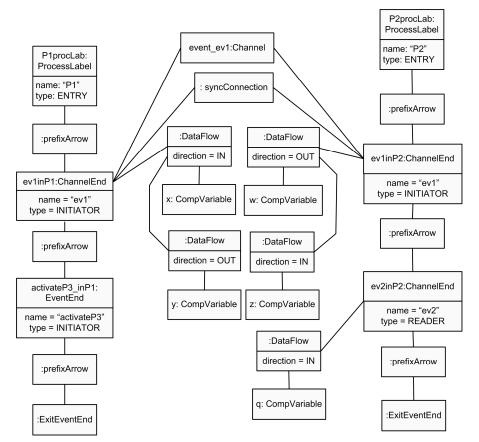

|   | 3.3.2      | Synchronization events and data flow                            | .71  |

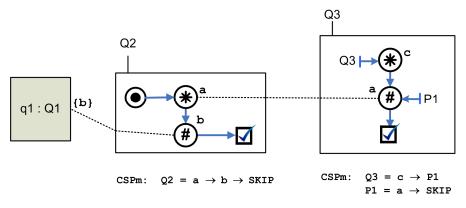

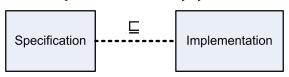

|   | 3.3.3      | Refinement operator                                             | . 72 |

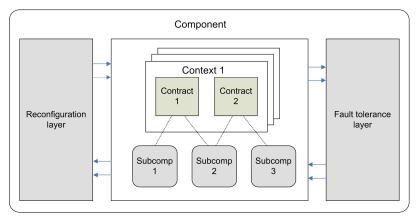

|   | 3.4        | INTERACTING COMPONENTS                                          | .72  |

|   | 3.4.1      | Structural units                                                | .72  |

|   | Co         | mponents                                                        | . 72 |

|   |            | rts and interfaces                                              |      |

|   |            | eraction Contracts                                              |      |

|   |            | ntexts                                                          |      |

|   | 3.4.2      | Interaction and control-flow diagrams                           |      |

|   |            | Discussion                                                      |      |

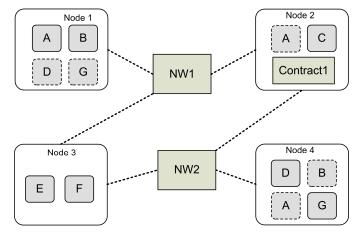

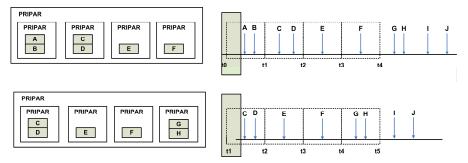

|   | 3.5        | DISTRIBUTED SYSTEMS – ALLOCATION                                |      |

|   | 3.6        | RELATED WORK                                                    |      |

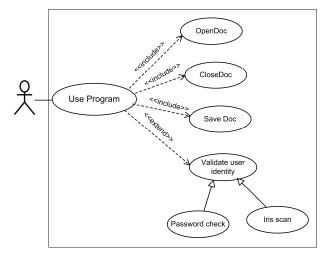

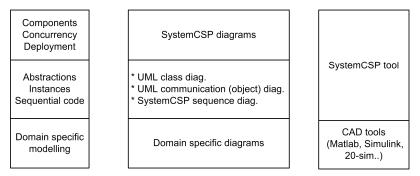

|   | 3.6.1      | SystemCSP vs. UML                                               |      |

|   | 3.6.2      | SystemCSP vs. GML                                               |      |

|   | 3.7        | POSITIONING                                                     |      |

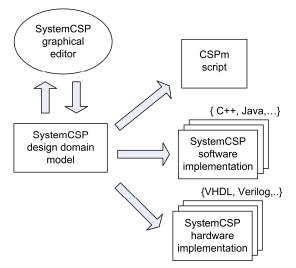

|   | 3.8        | IMPLEMENTATION                                                  |      |

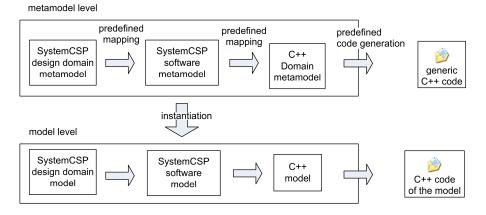

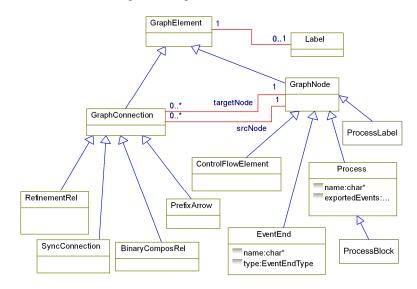

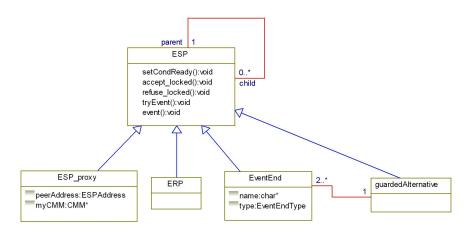

|   |            | etamodel of the notation                                        |      |

|   |            | apping to software domain                                       |      |

|   | 3.9        | CONCLUSIONS                                                     | .88  |

| 4 | REAL-TIME AND CSP                                                         | 91  |

|---|---------------------------------------------------------------------------|-----|

|   | 4.1 SPECIFICATION OF TIME PROPERTIES                                      | 91  |

|   | 4.1.1 Discrete time event ' tock'                                         |     |

|   | 4.1.2 Timed CSP                                                           |     |

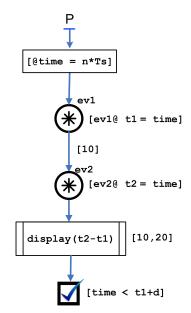

|   | 4.1.3 Time specification in SystemCSP                                     |     |

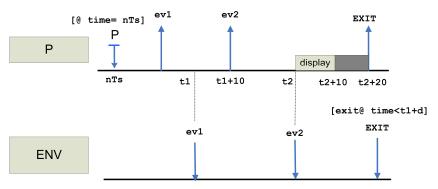

|   | Time specification in control flow diagram                                |     |

|   | SystemCSP time diagrams                                                   |     |

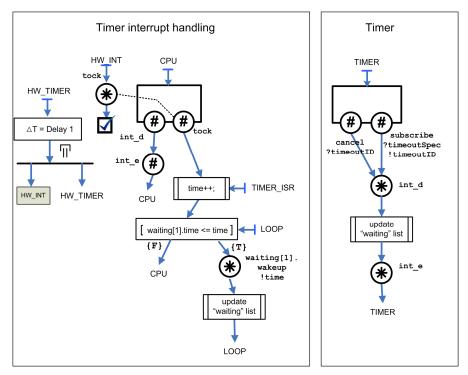

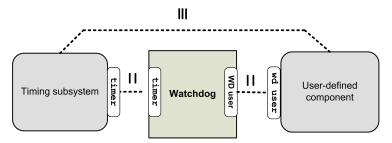

|   | Timing subsystem                                                          |     |

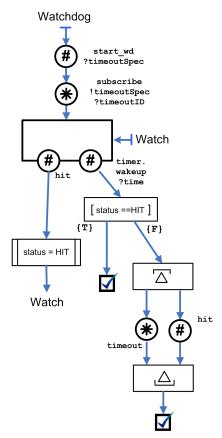

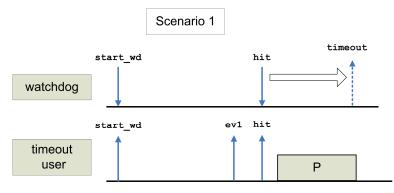

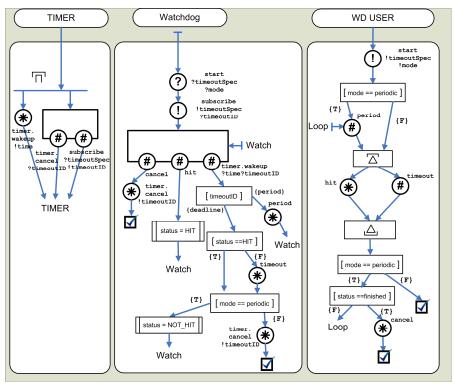

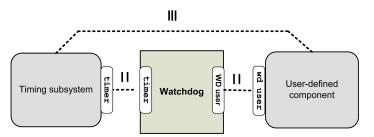

|   | Watchdog Design Pattern                                                   |     |

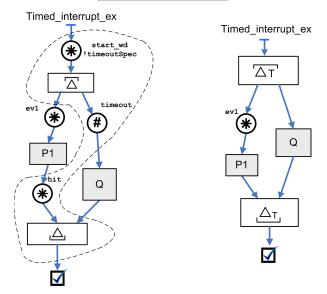

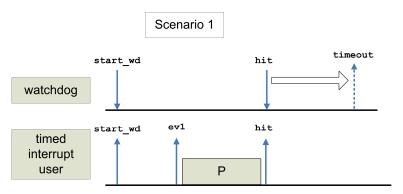

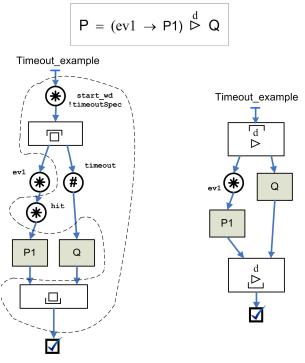

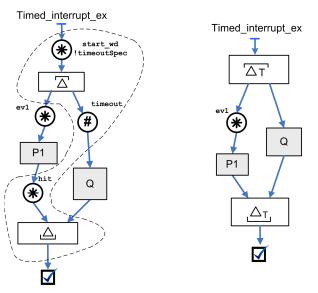

|   | Timed interrupt operator                                                  |     |

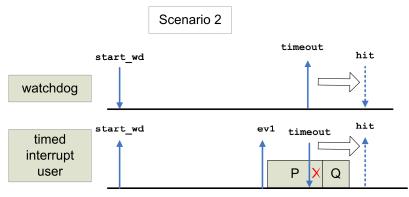

|   | Timeout operator                                                          | 100 |

|   | 4.2 REAL-TIME IN THE IMPLEMENTATION OF CSP-BASED SYSTEMS                  | 102 |

|   | 4.2.1 Identifying problems                                                | 102 |

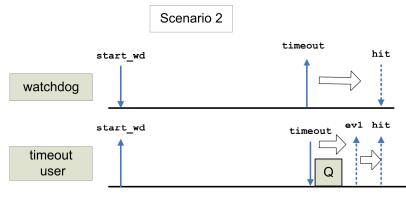

|   | Origin of time constraints in implementation of control systems           |     |

|   | Scheduling theories                                                       |     |

|   | Fundamental mismatch between CSP and classical scheduling - communicat    |     |

|   | induced precedence constraints                                            |     |

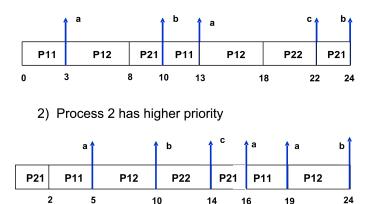

|   | Influence of assigning priorities on analysis                             |     |

|   | 4.2.2 Classic scheduling approach                                         | 108 |

|   | Priority inversion and using a buffer process to solve it                 | 108 |

|   | Absolute versus relative specification of priorities                      | 109 |

|   | RM                                                                        |     |

|   | EDF                                                                       |     |

|   | EDF*                                                                      |     |

|   | Design with rendezvous channel communication, convert them to shared data |     |

|   | objects when necessary                                                    |     |

|   | 4.2.3 Event based approaches                                              |     |

|   | Event-based scheduling                                                    |     |

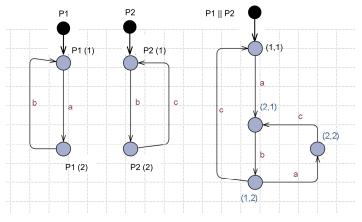

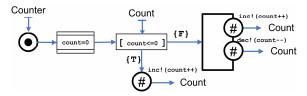

|   | Equivalent automaton                                                      |     |

|   | <ul><li>Mapping time properties to equivalent automata</li></ul>          |     |

|   | 4.5 CONCLUSIONS                                                           | 120 |

| 5 | DESIGN PATTERNS IN SYSTEMCSP                                              | 121 |

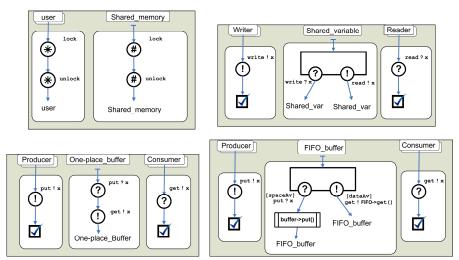

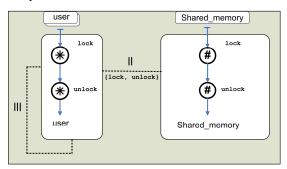

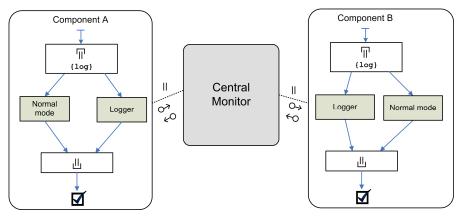

|   | 5.1 Communication patterns                                                | 122 |

|   | Design patterns – goals and ideas                                         |     |

|   | Design description                                                        |     |

|   | Remarks                                                                   |     |

|   | 5.2 PATTERNS RELATED TO COMPONENTS                                        |     |

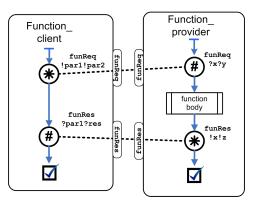

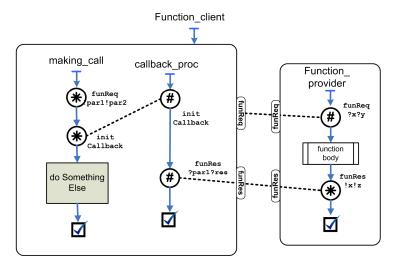

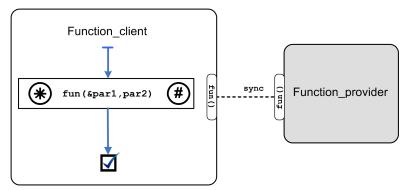

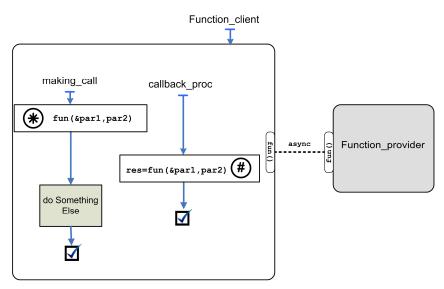

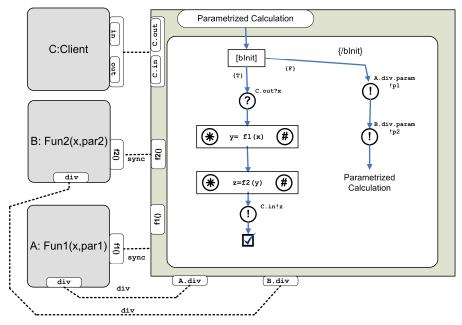

|   | 5.2.1 Inter-component function calls                                      |     |

|   | Design patterns – goals and ideas                                         |     |

|   | Design description                                                        |     |

|   | Remarks                                                                   |     |

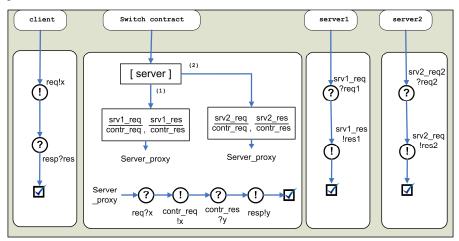

|   | 5.2.2 Switch interaction contract                                         |     |

|   | Design pattern – goals and ideas                                          |     |

|   | Design description                                                        |     |

|   | Remarks                                                                   |     |

|   | 5.2.3 Diversity interfaces                                                |     |

|   | Design pattern – goals and ideas                                          |     |

|   | Design description                                                        |     |

|   | Remarks                                                                   |     |

|   | 5.3 PATTERNS RELATED TO CONTROL SYSTEMS                                   |     |

|   |                                                                           |     |

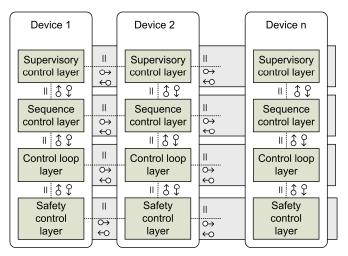

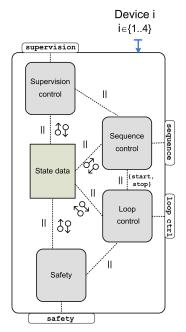

| 5.3.1 Layered structure of control systems                                                                                                                                                                                                                                                                                                                                                                                                                                                | 132                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 132                                                                                            |

| Design description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

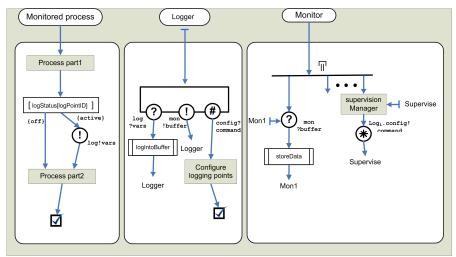

| 5.3.2 Supervision and monitoring layer                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 135                                                                                            |

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135                                                                                            |

| Design description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

| 5.4 FAULT TOLERANCE PATTERNS                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |

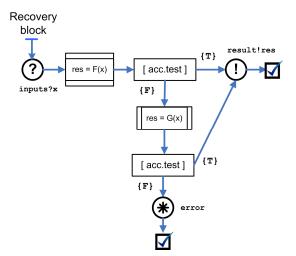

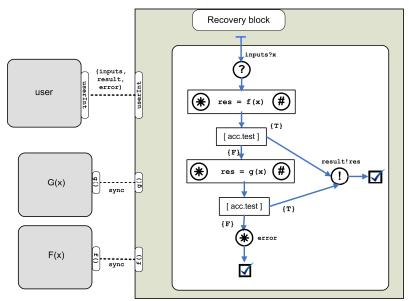

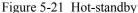

| 5.4.1 Recovery block                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                |

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| Design description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

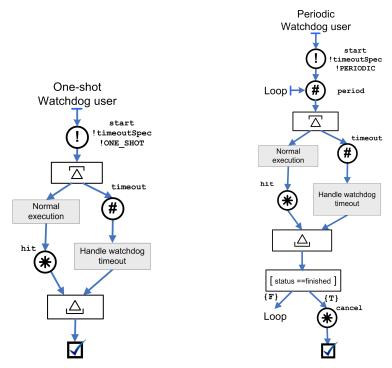

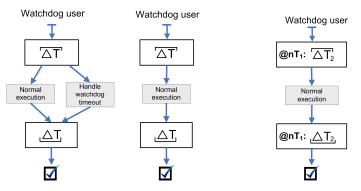

| 5.4.2 Watchdog design pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                |

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| Design description<br>Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                |

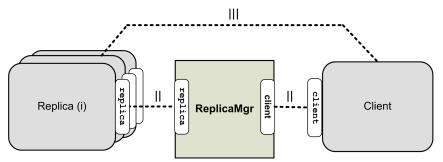

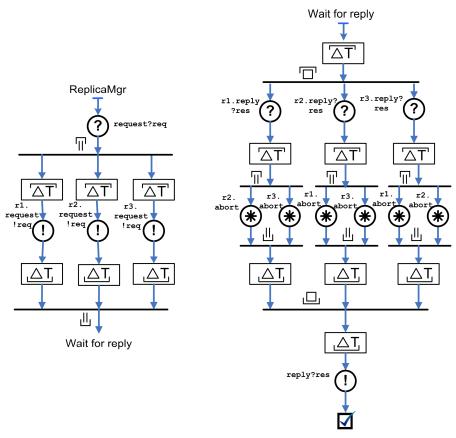

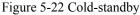

| 5.4.3 Replica Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| Design description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

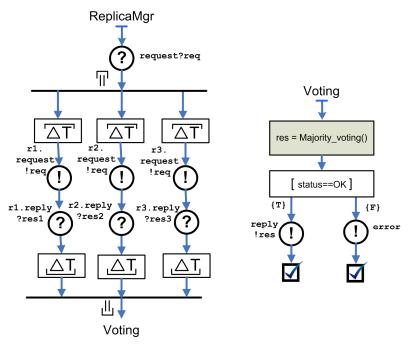

| 5.4.4 Exception Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| Design description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

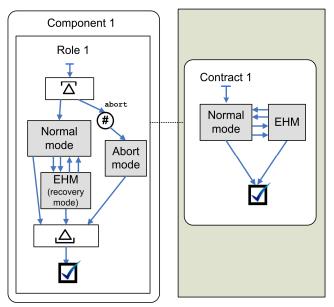

| 5.4.5 Checkpointing                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

| Design pattern – goals and ideas                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| Design description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

| 5.5 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 150                                                                                            |

| PRODUCTION CELL SETUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 151                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.50                                                                                           |

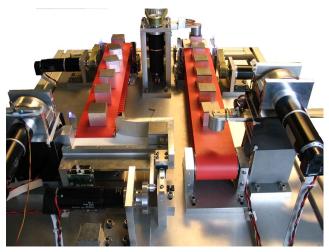

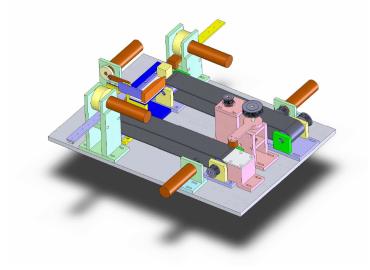

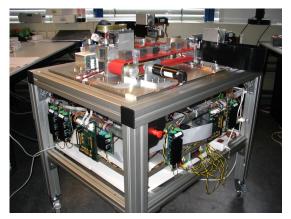

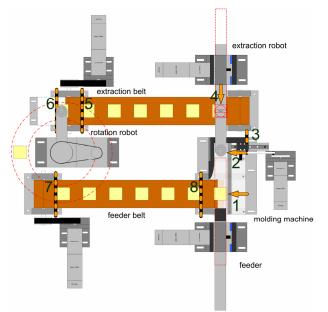

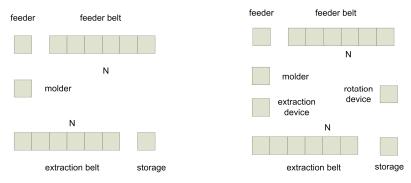

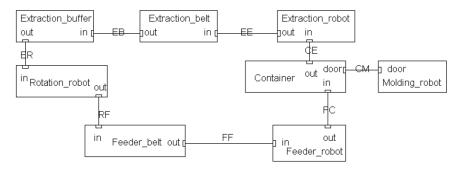

| 6.1 PRODUCTION CELL SETUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                |

| Purpose and properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 153                                                                                            |

| Purpose and properties<br>Detailed description                                                                                                                                                                                                                                                                                                                                                                                                                                            | 153<br>154                                                                                     |

| Purpose and properties<br>Detailed description<br>Structural deadlock                                                                                                                                                                                                                                                                                                                                                                                                                     | 153<br>154<br>155                                                                              |

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE                                                                                                                                                                                                                                                                                                                                                           | 153<br>154<br>155<br>156                                                                       |

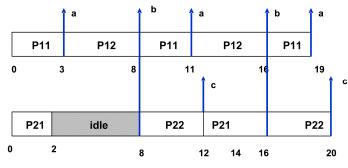

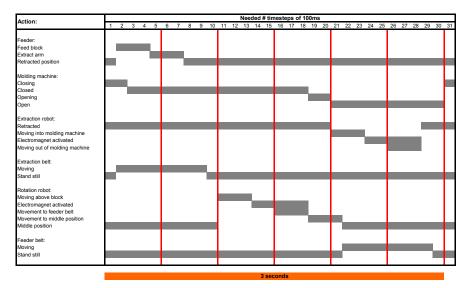

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach                                                                                                                                                                                                                                                                                                             | 153<br>154<br>155<br>156<br><i>157</i>                                                         |

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design                                                                                                                                                                                                                                                                   | 153<br>154<br>155<br>156<br>157<br>157                                                         |

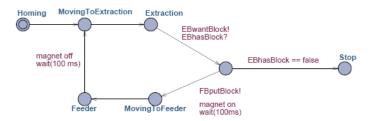

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL                                                                                                                                                                                                                                         | 153<br>154<br>155<br>156<br>157<br>157<br>160                                                  |

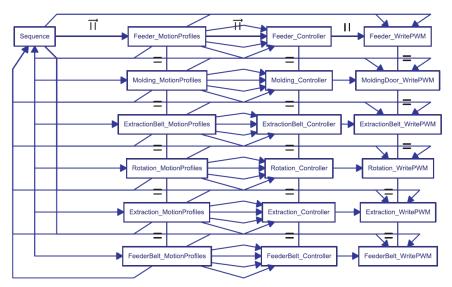

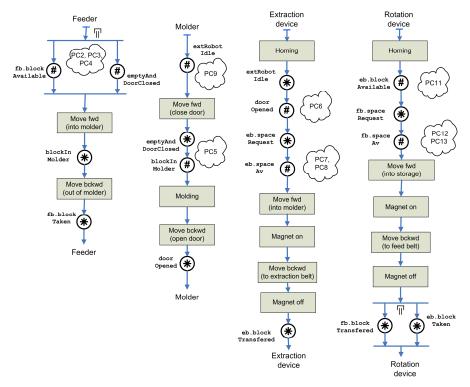

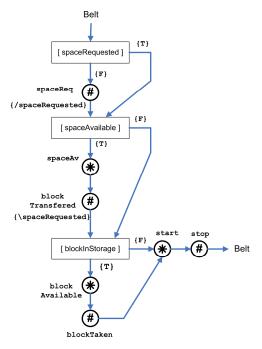

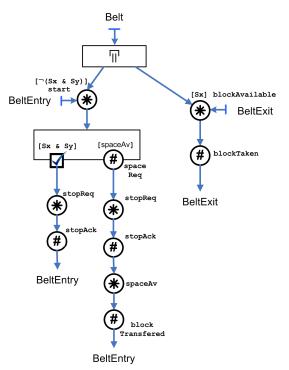

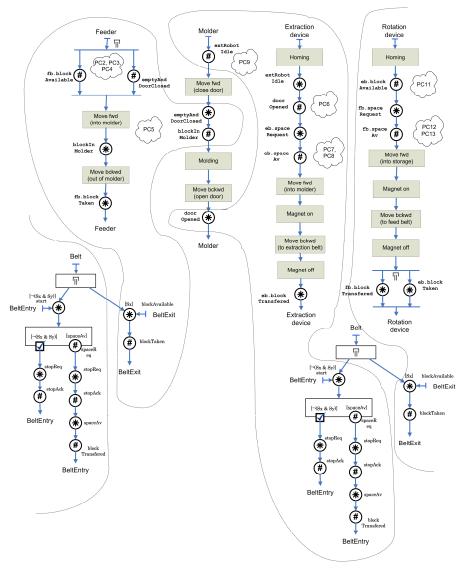

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN                                                                                                                                                                                    | 153<br>154<br>155<br>156<br>157<br>157<br>160<br>161                                           |

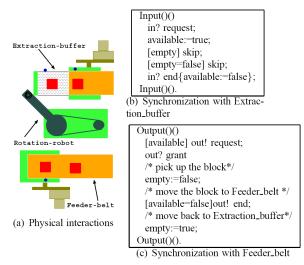

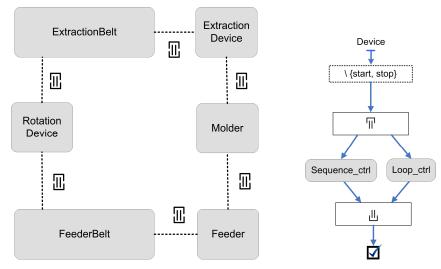

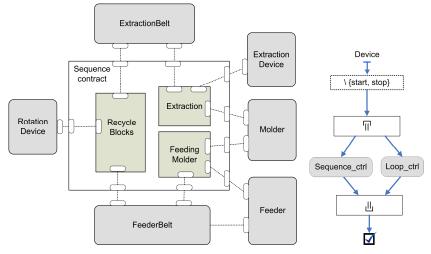

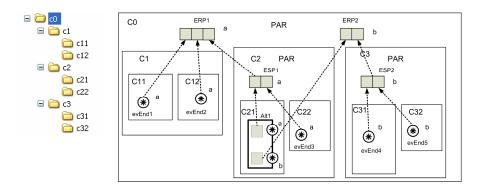

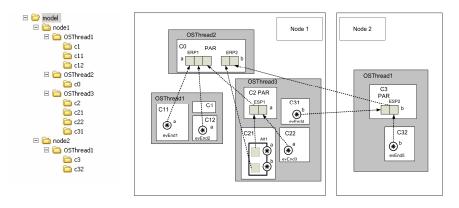

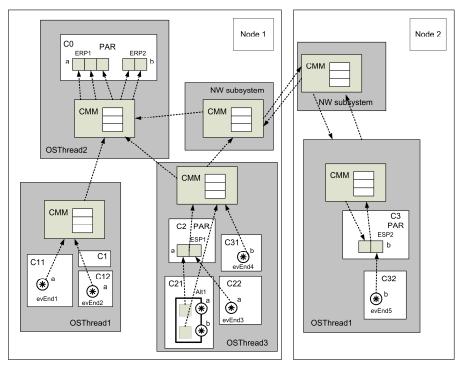

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure                                                                                                                                               | 153<br>154<br>155<br>156<br>157<br>160<br>161<br>161                                           |

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Basic structure                                                                                                 | 153<br>154<br>155<br>156<br>157<br>167<br>161<br>161<br>161                                    |

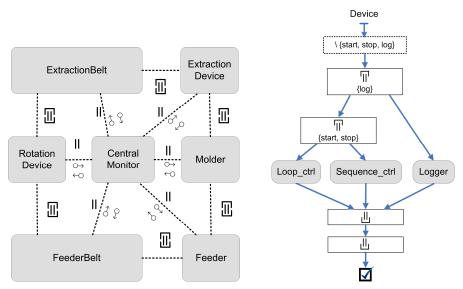

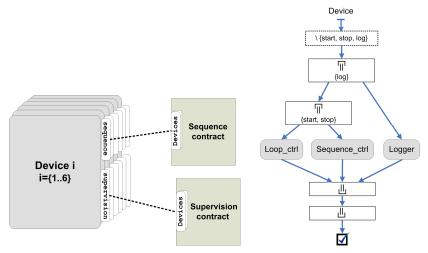

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Adding monitoring layer                                                                                         | 153<br>154<br>155<br>156<br>157<br>160<br>161<br>161<br>161<br>162                             |

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Adding monitoring layer         Assigning priorities                                                            | 153<br>154<br>155<br>156<br>157<br>167<br>161<br>161<br>161<br>162<br>163                      |

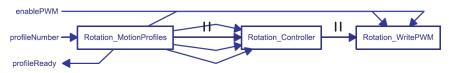

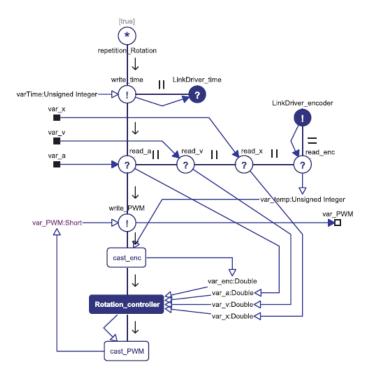

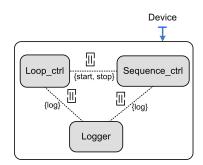

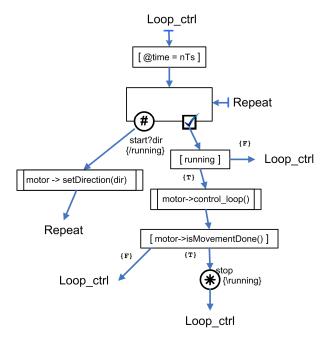

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Adding monitoring layer         Assigning priorities       6.3.2         6.3.2       Loop controllers           | 153<br>154<br>155<br>156<br>157<br>167<br>161<br>161<br>161<br>162<br>163<br>163               |

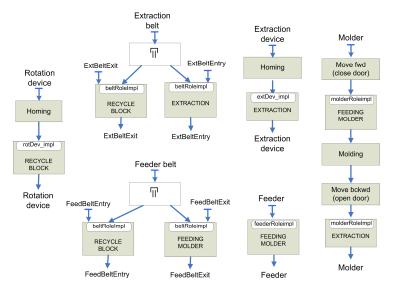

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Adding monitoring layer         Assigning priorities       6.3.2         Loop controllers       Structural part | 153<br>154<br>155<br>156<br>157<br>160<br>161<br>161<br>161<br>163<br>163<br>163               |

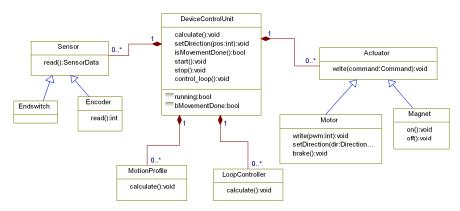

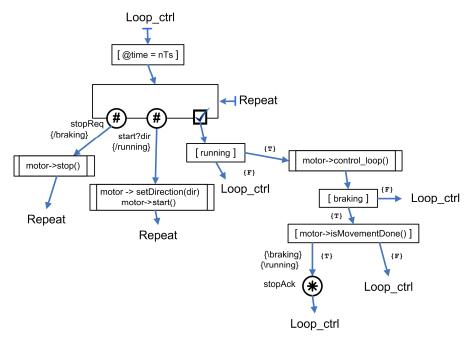

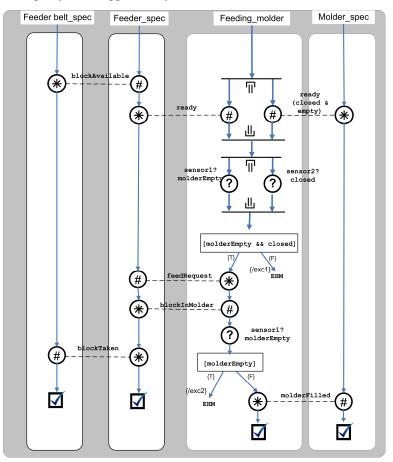

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Adding monitoring layer         Assigning priorities                                                            | 153<br>154<br>155<br>156<br>157<br>160<br>161<br>161<br>161<br>163<br>163<br>163<br>163<br>165 |

| Purpose and properties         Detailed description         Structural deadlock         6.2       OTHER WAYS TO DESIGN SOFTWARE         6.2.1       Time-table based approach         6.2.2       GML/CT library design         6.2.3       POOSL         6.3       SYSTEMCSP - DEVICE-ORIENTED DESIGN         6.3.1       System structure         Basic structure       Adding monitoring layer         Assigning priorities       6.3.2         Loop controllers       Structural part | 153<br>154<br>155<br>156<br>157<br>160<br>161<br>161<br>161<br>163<br>163<br>163<br>165<br>166 |

6

|   |     | Dependencies                                              |  |

|---|-----|-----------------------------------------------------------|--|

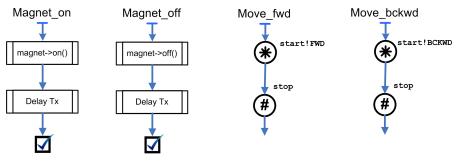

|   |     | Generic sequence control                                  |  |

|   |     | Time based schedule                                       |  |

|   |     | Sensor based sequence control                             |  |

|   |     | Event based sequence control                              |  |

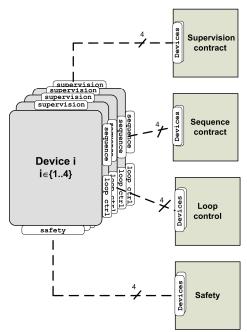

|   | 6.4 | INTERACTION CONTRACT BASED DESIGN                         |  |

|   | 6.5 | CONCLUSIONS                                               |  |

| 7 | С   | ONCLUSIONS AND RECOMMENDATIONS                            |  |

|   | 7.1 | CONCLUSIONS                                               |  |

|   | 7.  | 1.1 Summary                                               |  |

|   |     | SystemCSP core elements                                   |  |

|   |     | Real-time support                                         |  |

|   |     | Design patterns in form of reusable interaction contracts |  |

|   |     | Complex control system test case                          |  |

|   | _   | Implementation issues                                     |  |

|   | 7.  | 1.2 Evaluation                                            |  |

|   |     | Mapping to some existing formal verification method       |  |

|   |     | Support for specification and analysis of time properties |  |

|   |     | Support for component-based development                   |  |

|   |     | Expressiveness and readability                            |  |

|   |     | Scalability<br>Unambiguous interpretation                 |  |

|   |     | Applicability to complex control systems                  |  |

|   |     | Conclusion                                                |  |

|   | 7.2 | RECOMMENDATIONS AND OPEN ISSUES                           |  |

|   | 1.2 | Tooling                                                   |  |

|   |     | Mapping to hardware domain                                |  |

|   |     | Distribution                                              |  |

|   |     | Simulation                                                |  |

|   |     | Software implementation                                   |  |

|   |     | Usage                                                     |  |

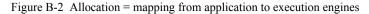

| A | Μ   | IETAMODELS                                                |  |

|   | A.1 | METAMODELS AS BASIS FOR CODE GENERATION                   |  |

|   | A.2 | METAMODEL OF SYSTEMCSP DESIGN DOMAIN                      |  |

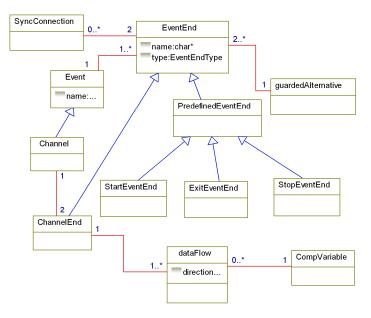

|   | A.  | 2.1 Event ends                                            |  |

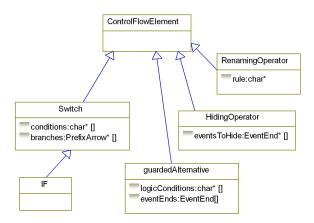

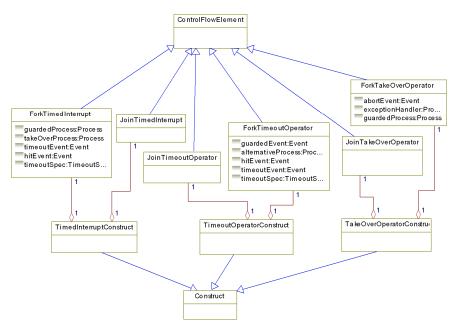

|   |     | 2.2 Control flow elements                                 |  |

|   |     | Elements with direct mapping to CSP                       |  |

|   |     | Start/exit control flow elements.                         |  |

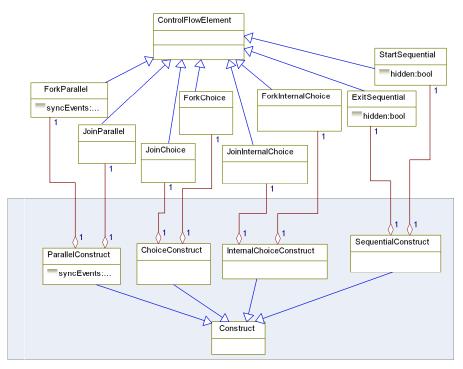

|   |     | Advanced fork/join control flow elements                  |  |

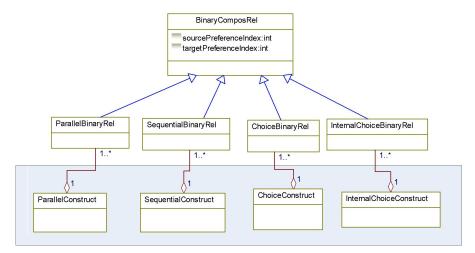

|   | А.  | 2.3 Binary compositional relationships                    |  |

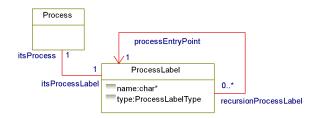

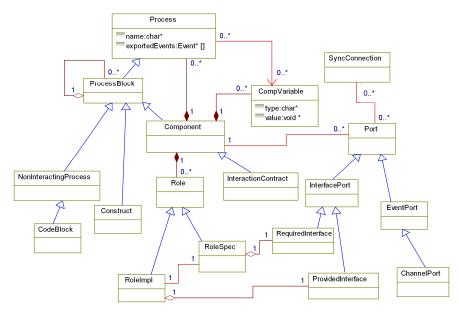

|   |     | 2.4 Components and processes                              |  |

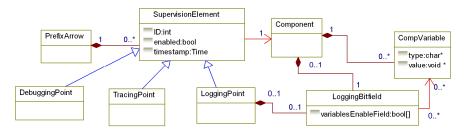

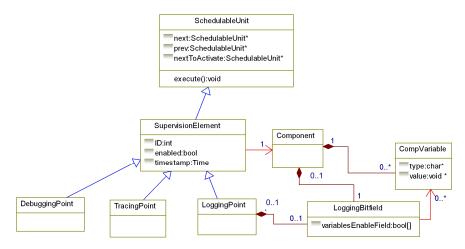

|   |     | 2.5 Supervision elements                                  |  |

| B | S   | OFTWARE FRAMEWORK DESIGN                                  |  |

|   | B.1 | WHY YET ANOTHER CSP LIBRARY?                              |  |

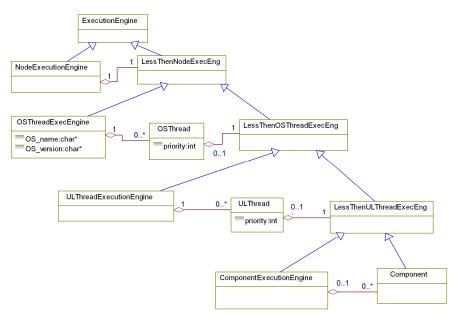

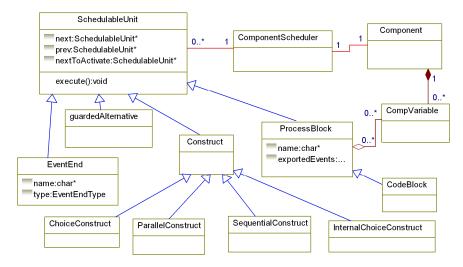

|   | B.2 | EXECUTION ENGINE FRAMEWORK                                |  |

|   |     | Brief overview of execution engines                       |  |

|   |     | Discussion                                                |  |

|   |     | Four- layer execution engine architecture                 |  |

|   |     |                                                           |  |

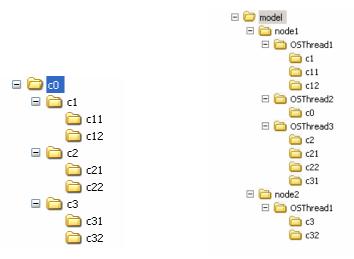

|            | Allocation                                          |     |

|------------|-----------------------------------------------------|-----|

|            | Priority assignment                                 |     |

|            | Components, processes and variables                 |     |

|            | Function call-based concurrency inside components   |     |

| B.3        | IMPLEMENTING CSP EVENTS AND CHANNELS                |     |

|            | Event synchronization mechanism                     |     |

|            | Solving the mutual exclusion problem                |     |

|            | Channels capable for multidirectional communication |     |

|            | Distribution/networking                             |     |

| B.4        | OTHER PARTS OF THE SOFTWARE DESIGN                  |     |

|            | Exception handling                                  |     |

|            | Logging                                             |     |

|            | Tracing                                             |     |

| B.5        | Conclusions                                         |     |

| REFERENCES |                                                     | 231 |

| CURRI      | CULUM VITAE                                         |     |

#### Acknowledgment

The author would first like to thank his supervisors, colleagues and students at the Control Laboratory. Next, the author thanks his family and friends for their support during this work. Finally, the author thanks to life.

Bojan Orlić

#### Summary

Realization of embedded control systems is a complex task. Increasing part of this complexity is nowadays located in the design and implementation of software that runs them. A major source of difficulties is the limitation of the average software developer to understand and design complex behavioral scenarios. A big part of this complexity comes from the interaction of concurrently existing entities.

Similar to the way energy-flow based modeling is used in bond-graph theory as a common view in multi-domain physical system modeling, in our approach concurrency is viewed as a glue layer that relates different domains and views. Concurrency used in a structured way should lead to systems that are simple to design and understand, easy to distribute, reconfigure and reuse.

The aim of this thesis is to develop a graphical design specification language that can offer a structured way of handling concurrency. A structured way of using concurrency is expected to raise the abstraction level away from concurrency problems. In that way, the introduced design specification language should become a vehicle for reducing complexity in inherently concurrent systems (e.g. complex control systems).

Our approach is not to invent the wheel all over again. Instead, we want to build upon the existing body of knowledge provided by relevant formal methods.

SystemCSP is based on the principles of both component-based design and CSP process algebra. It is applicable for specifying, documenting, visualizing and formal verification of component-based designs. It provides a way to visualize architecture, behavioral patterns of components, intra–component interactions and execution relations among components.

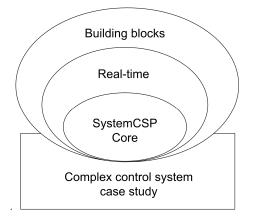

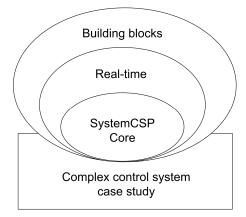

First, the elements of the language are introduced. Than, this core set of language elements is extended with elements dedicated to the specification of time properties. The thesis also offers some insights and some possible approaches for analysis and implementation of real-time systems. The core of the notation is further extended by introducing a set of higher-level primitives in the form of reusable design patterns (see Figure 1-6). These patterns can be used in designs as basic building blocks, extending in that way the vocabulary and raising the level of abstraction of design processes.

The usability of the notation for specifying interactions in embedded control systems is tested by designing software for a complex control setup consisting of several cooperating devices. This test case is a step towards industrial-strength setups.

SystemCSP seems to be convenient way to specify interactions in concurrent component-based embedded control systems.

# 1 Introduction

The greatest challenge to any thinker is stating the problem in a way that will allow a solution.

#### **Bertrand Russell**

Making embedded control systems is a multidisciplinary activity. It includes physical system modeling in various domains (e.g. mechanical, electrical, chemical, and thermodynamic), designing control algorithms, and implementing them in software programs. This research is focused on the software implementation part.

Compared to conventional programming, the software development in area of embedded control systems is somewhat specific. The embedded control systems application area does introduce somewhat more stringent constraints. For instance, there is a need for more rigorous verification of functional and timing properties. A need for performance optimization is additionally increased due to massproduction and related needs for minimizing software/hardware costs per unit and minimizing time-to-market.

Existing control-domain related CAD tools do provide solid code generation support for the software implementation of control laws. However, building complex control systems, where event based interaction between concurrently existing components is very important, is not primary concern of such tools. Attempt to apply the methods, the design specification languages, and the tools from general software development, turns out to be problematic with respect to timing predictability, structuring concurrency, minimizing costs, and optimizing performance.

This research introduces SystemCSP, a graphical language for design specification of concurrent, component-based embedded control systems. SystemCSP is designed to be an expressive, readable, and structured way to design interactions of concurrently existing components. It is based on the CSP formal algebra. The relevant application area for this language is in practical implementations of distributed real-time control systems. The proposed design specification language can, as well, be used in other software development domains where concurrency is inherently present and where focus is on interaction of concurrently existing components.

This chapter starts with introducing some of the key concepts of the research context. Throughout this chapter, instead of providing strict definitions, the chosen approach is to provide descriptions that will allow a reader unfamiliar with the used terms to grasp their meaning and create intuitive representation of the key notions. Section 1.1 of this chapter briefly identifies some notions from the control systems application area. Brief description of the current state of the art, concepts and problems in software engineering area is the topic of section 1.2. Section 1.3 attempts to address issues like: somewhat more detailed problem statement, brief

exploration of previous attempts to solve it, setting demands on language features and sketching the basic ideas and principles behind the SystemCSP language. Finally, section 1.4, gives a short outline of the complete thesis.

### 1.1 Control systems application area

The success of human evolution is mainly due to human's ability to understand, model, control and adapt their environment.

*Modeling* is a process of creating an abstracted description of reality. The aim of the modeling process is to identify a competent model - the simplest model that captures, with sufficient accuracy, all aspects of the system behavior relevant for the problem at hand. The purpose of the modeling process is gaining insight in the way real entities behave. This insight can later serve as a basis for controlling the modeled system by manipulating some of its variables.

A *control system* (controller) can be seen as a component added to a system (plant) that needs to be controlled. The essence of control is to maintain the desired values of certain system variables by manipulating values of input variables of the controlled system.

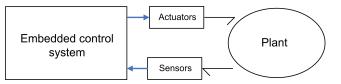

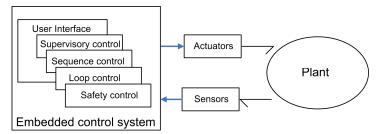

A *control system* interacts with its environment via various *sensors* and *actuators*. Sensors convert physical signals to signals understandable by the *control system* (digital quantities in case of computer-based control). Actuators (motors, valves and so on) perform the transformation in the opposite direction (see Figure 1-1). In Figure 1-1 the different types of arrow symbols are used for digital and analogue signals.

Figure 1-1 Typical control system (Figure based on (Broenink and Hilderink, 2001))

At first, design models of plants and control systems were captured on paper-like media and controllers were realized using mechanics and analog electronics. Application of computers brought more flexibility in the areas of modeling and real world implementation of control systems. With computers, it became easily possible to adapt parameters and algorithms of control systems during system usage. An even more important gain is the opportunity to easily simulate the behavior of a complete system and thus obtain valuable insights into its behavior while remaining purely in the virtual world.

*Simulation* is the process of exploring the behavior of some system through the execution of its model according to the related operational semantics. Different initial conditions lead to different traces through the state-space of a simulated system. System parameters can be modified in a controlled way and their influence on the overall system behavior can be estimated.

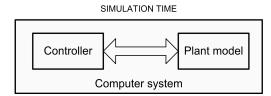

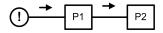

Figure 1-2 Simulation

Figure 1-2 illustrates co-execution of the model representing a control component ('Controller block' in Figure 1-2) and the one representing the controlled system ('Plant model' block in Figure 1-2). In simulations, the time flow is a property of the simulated system and as such independent of real clock time.

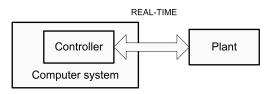

Unlike in simulation, in the interaction with a real plant (see Figure 1-3) the control system has to keep pace with the progress of real time. The combination of software and hardware that is implementing the control system, should be designed to guarantee proper temporal properties of the complete system. Simulation can give some insight in the time behavior of the system. Still, only real-time analysis can guarantee satisfaction of temporal constraints. A special branch of computer science (*'real-time* systems' and related 'real-time scheduling theories') is dedicated to the task of real-time analysis.

Figure 1-3 Real system

In real-time systems, "correctness of the system depends not only on the logical result of the computation but also on the time at which results are produced" (Buttazzo, 2002). In those systems, the response should take place in a certain time window. Real-time is not about the speed of the system, but rather about its relative speed compared to the required speed of its interaction with the environment. Rather then fast, the response of those systems should be predictable in sense that a guarantee can be given that the response will fall in the predefined time window. A fast system will not be real-time if its environment is requiring a faster response. A controller implemented with slow computer system can work in real-time if it is faster than the response that the controlled plant requires.

*Concurrency* is one of the most essential properties of the real world. We can perceive that many activities take place simultaneously. Obviously, a (control) system and its relevant environment (plant) exist concurrently. In fact, both plant and control system are often decomposed into smaller parts existing concurrently and cooperating to achieve a desired behavior. The main source of complexity in designed systems stems actually from the simultaneous (concurrent) existence of many objects, events and scenarios. Better control over the concurrency structure,

should therefore automatically reduce the problem of complexity handling. Thus, a structured way to deal with concurrency is needed.

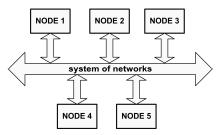

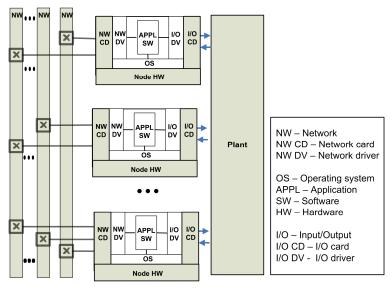

Figure 1-4 Distributed computer platform

This research puts focus on concurrency applied to control systems implemented on top of distributed computer platforms. By the term *distributed computer platform*, we will assume a system built on top of a hardware topology consisting of several computing nodes interconnected via some kind of network, as illustrated in Figure 1-4. In the control systems application area, the most commonly used network interconnections are fieldbuses. The term *fieldbus* is a common name for a set of various serial data communication protocols used in control and instrumentation system architectures.

Figure 1-5 Control system based on distributed computer platform

In distributed systems, tasks residing on different nodes execute truly in parallel. For studying concurrency phenomena (deadlock, livelock, race hazard, etc.) of a system, it is not relevant whether its concurrent execution is truly parallel or parallelism is only mimicked via some kind of CPU scheduling. However, for studying the real-time behavior of the system, issues like allocation of tasks to nodes, processing capabilities of the nodes, network delay times and applied scheduling algorithms become relevant.

Control systems as the one depicted in Figure 1-1 are often implemented on top of distributed computer systems (see Figure 1-4). Distributed computer system specialized for the implementation of control systems is typically based on a hardware/software platform that has a topology like the one depicted in Figure 1-5.

In addition to network interconnections between nodes, it contains input/output (I/O) interfaces as points where a control system can use actuators to exert influence on a plant, or sensors to observe changes in some of the plant's signals.

#### **1.2 Software development practice**

Since its very beginning, software development is located somewhere in the middle between art, craft and engineering. A major source of difficulties is the limitation of the average software developer to understand and design complex behavioral scenarios.

The current state of the art in the software development area is still marked by the *software crisis* phenomena (Dijjkstra, 1972). *Software crisis* is a term used to denote the incapability of existing methodologies, programming languages and tools to offer adequate support for development of complex software programs.

Ever increasing demands on additional features and performance resulted in increased complexity of developed software systems. There is a constant need to decrease production costs and development time. Teamwork does not scale well, because partitioning into subsystems and their later integration is not always trivial. As a result, software projects are often late and adding more man power makes them often even more late. Verification and debugging of complex systems is difficult. (Keding, 2004)

In the embedded system area, due to cost-efficiency needed for mass production, resources used per product are minimized. This results in an increased effect of the software crisis. Additionally, in embedded systems, non-functional requirements like: performance, reliability, maintainability, safety, fault tolerance, security and power consumption are often of equal or higher relevance then just producing correct results. In addition, standards and algorithms applied are constantly changing, necessitating implementation of flexible and upgradeable architectures.

All these problems illustrate a need for introduction of a novel design methodology. The design methodology should offer a way to structure complexity of the system in a way that efficiently utilizes human comprehension capabilities. A good idea could be abstracting away from the hardware/software development domain, allowing in that way that most of the design is performed at system level and postponing hardware/software allocation to later phases.

#### 1.2.1 Structured approaches

All major advances in software development are actually in some way extending human capabilities to deal with complexity. Most often, this is achieved by raising the abstraction level and introducing some notion of hierarchy. In the beginning, programs were written in low-level machine and assembly code. Subsequently the view of a programmer was lifted to higher abstraction levels in several phases: the concept of *operating systems*, the introduction of high-level programming languages, and finally, the modern *object-oriented* approach. *Object-oriented programming* (OOP) has added, to the world of software development, many concepts comparable to the way the human mind operates.

Complex software implemented by an immediate 'coding and fix' ad-hoc approaches is bound to fail. Often it is compared to making a building without any prior plans and calculations (Booch, 1993). Like a properly designed building has a certain architecture corresponding to the requirements of the end users, the same can be said for a properly designed software system. Instead of the 'nothing works' until everything works' approach, iterative incremental design is often suggested (Booch, 1993).

One of the structured approaches to software design is based on reusing *design patterns* as common solutions to recurring problems. Design patterns (Gamma et al., 1994) systematically name, explain and evaluate important and recurring designs in order to capture them in a form that can be reused effectively. Besides this design description, a pattern contains a description of the problem and the context where it is applicable, as well as the results and trade-offs emerging from its application.

A *software architecture* is a set of high-level design decisions regarding the employed components and the way they are composed and connected. Design decisions left to downstream architects and implementers are not considered part of the architecture on the current abstraction level (McConnell, 2003).

Software architectures are often based on components. A *component* is a unit of composition with contractually specified interfaces and fully explicit context dependencies that can be deployed independently and is subject to third-party composition (Szyperski, 1998).

Thus, a new design methodology, that aims to respond to the problems in current software development practice, should be capable to reduce complexity by imposing more structure in system design. Design patterns and component-based approach seems to offer a structured way to efficiently approach designing complex software architectures.

#### Visual programming

It is well known that visual information is easier to understand. Obviously, any design methodology will benefit from being based on a visual notation that is intuitively clear and self-explaining. Engineers often need to visualize their designs in order to obtain better understanding and also to be able to share that understanding with other members of the team. As a natural consequence, a class of visual modeling languages has emerged. More and more tools are developed with an aim of providing a graphical modeling language for entering designs. Most of the tools are also able to generate source code and/or executables from such

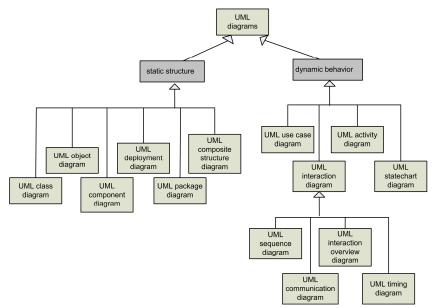

models. Some of the popular commercially available tools belonging to this category are Labview, Rhapsody, Rational Rose, Matlab/Simulink, dSpace, 20-sim, etc. A distinction can be made between domain specific (e.g. control systems) CAD (*Computer Aided Design*) tools (Matlab/Simulink, Labview, dSpace, 20-sim, etc.) and the more general CASE (*Computer-Aided Software Engineering*) tools intended for modeling software designs (Rhapsody, Rational Rose, etc.). The latter category most often relies on the UML graphical modeling language, which is the de facto industry standard for designing software systems.

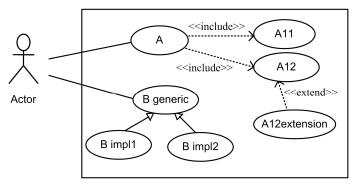

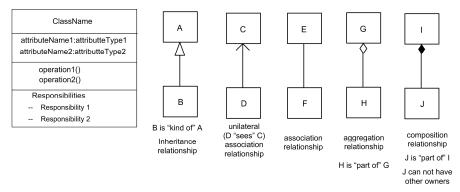

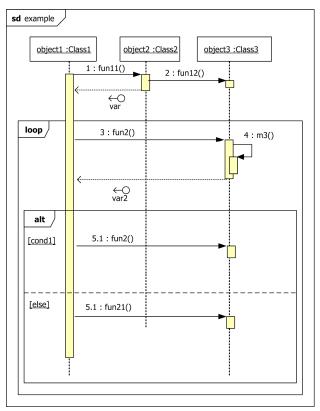

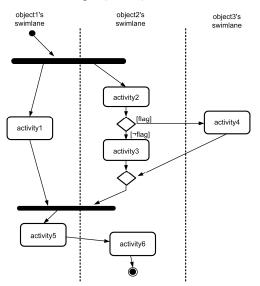

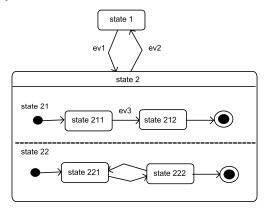

"The Unified Modeling Language (UML) is a general-purpose visual modeling language that is used to specify, visualize, construct, and document the artifacts of a software system" (Booch at al., 1999). It is tightly coupled to the Object-oriented programming (OOP) design philosophy. UML is a general modeling language. Its capability to model abstractions and structural relationships between them, regardless of the domain, makes it suitable for defining a domain vocabulary and basic structural laws of the domain (i.e. it is suitable for defining a metamodel of the domain). UML offers several kinds of diagrams that allow insight in the system structure and behavior from different viewpoints. The main disadvantage of UML is the lack of a glue layer able to connect all views into a consistent model of the system. In addition, a rigorous software engineering approach would require that such a glue layer is amenable to formal verification.

#### **Formal verification**

In all non-trivial projects, a significant part of product development time is spent on verification. Most of redesign is still caused by functional errors that could have been fixed with proper verification (Keding, 2004). Informal verification relies on performing a large quantity of custom, application-specific tests. *Formal verification* performs property checking based on mathematical techniques and precise requirements. In practice, the general weakness of formal verification tool implementations lies in the computational complexity (also referred to as "statespace explosion") needed to execute verification algorithms. Therefore, in practice *simulation* is often a main vehicle to verify complex systems. Computational complexity of verification analysis would be significantly reduced if a system could be hierarchically decomposed into separately verifiable building blocks. *Hierarchical verification* takes pre-verified blocks and focuses on block interconnections (which is usually a major source of problems).

It is desirable that designs are amenable to formal verification based on some mathematical formalism. Thus, a novel design methodology able to respond to the challenges of the software crisis should be related to some formal method capable to allow compositional hierarchical verification of the system.

#### Concurrency

Hardware vendors answer to increasing demands for processing power with parallel computer architectures— hyper-threading and multi-core multiprocessors. Software must be able to exploit these parallel hardware architectures in a both safe and efficient way (Sutter, 2005).

The computer science area, up to now, did not provide daily software development *practice* with an adequate response to the need for a simple and structured way of handling concurrency. Synchronization primitives offered by existing operating systems and programming languages are too low-level (Lee, 2006) and do not scale well with complexity (Hilderink, 2005a). Since the higher-level synchronization has to be designed for every problem in an ad-hoc manner, it is easy to unintentionally misuse those synchronization primitives. This usually results in problems that can stay hidden during most of the software lifetime and emerge in the worst possible moments.

The way concurrency is applied is getting more and more mature and structured. It is expected that a structured way of using concurrency will soon become mainstream and the most important breakthrough in software development after the invention of object-oriented programming. Many libraries, e.g. CT libraries (Hilderink et al., 1997; Orlic and Broenink, 2004), YAPI (Kock at al., 2000), Kent libraries (JCSP, 2007), design and development tools like Ptolemy (Eker et al., 2003), UPAAL (UPPAAL, 2007), gCSP (Jovanovic et al., 2004), SHESim/POOSL (2007) are based on various theories concerned with discrete event systems (Cassandras and Lafortune, 1999; Roscoe, 1997; Schneider, 2000; Milner, 1989; Kahn and MacQueen, 1977) in order to structure concurrency.

Obviously, as concurrency becomes a more and more important design issue, it should be easily expressible in terms of the ideal design methodology.

Concurrency is an unavoidable issue in managing complex software projects. Similar to the way energy-flow based modeling is used in bond-graph theory as a common view in multi-domain physical system modeling (van Amerongen and Breedveld, 2002), in our approach concurrency is viewed as a glue layer that relates different domains and views. Concurrency used in a structured way should lead to systems that are simple to design and understand, and easy to distribute, reconfigure and reuse. Furthermore, designs are expected to be revised step-by-step with formally verifiable conformance to the initial specification. Formal checking can ensure freedom from concurrency related hazards (like deadlocks, livelocks, and race conditions), that are otherwise hard to analyze and prevent in complex problems.

Many *formal methods* (Formal methods, 2007) and process algebras were introduced in order to bring mathematical rigor into the way concurrent systems are described and analyzed. For instance, CSP (Hoare, 1978; Roscoe, 1997; Schneider, 2000) is one of the first and most influential formal methods. It offers a relevant parallel programming model, and seems to be a promising choice for handling concurrency. A commercial powerful tool, FDR (Formal Systems, 2005), exists, that can provide support for formal checking CSP expressions.

CSP is also one of the rare formal methods, whose subset was used as a basis of a programming language, and thus applied in software development practice. Occam (INMOS, 1988) is a simple and easy to use parallel programming language designed on CSP principles. It implements a certain subset of CSP constructs and allows construction of programs that can be formally checked. Occam and its hardware companion, the transputer (Welch et al., 1993) were very powerful and

scalable tools for building complex distributed systems. The application area of control systems has seen many successful projects based on the combination of the two (Fleming, 1988; Sunter, 1994). But with transputers being outperformed by other microprocessors, occam also felt into oblivion. Actually, this is not completely true. Occam is used in several research environments (Hilderink, 2005a; JCSP, 2007; Welch and Wood 1996) as a role model in shaping the way of for structuring concurrency.

### 1.3 SystemCSP approach

#### 1.3.1 Problem statement

The aim of this thesis is to develop a graphical design specification language that can offer a structured way of handling concurrency. In accordance with previous text, a structured way of using concurrency is expected to raise the abstraction level away from concurrency problems. In that way, the introduced design specification language should become a vehicle for reducing complexity in inherently concurrent systems (e.g. complex control systems).

Key demands for such a design specification language are:

- Mapping to some existing formal verification method (this is necessary in order to provide support for formal verification without investing effort in creating new verification methods and tools)

- Support for specification of time properties and ways to analyze them (this is an essential demand stemming from the control systems application domain where timing properties are crucial)

- Support for modern notions of component-based development

- Expressiveness (it should be possible to easily express most important design decisions)

- Readability (the notation should be intuitive and easy to understand. It should be possible for a person familiar with the notation to grasp fast the key design decisions depicted in diagrams)

- Unambiguous interpretation of specified designs (the language is, in perspective, expected to result in a design tool with code generation facilities. Ambiguous interpretation would lead to uncertainty in the actual behavior of the implementation, making it dependent on tool vendors and the way in which code generation facilities are implemented.)

- Scalability (in order to be helpful in managing complexity, designs should scale well with increasing the number of used elements. In the language definition, this demand maps to the need for careful design of graphical elements and a well-thought balance between mandatory and

optionally visualized elements of the notation. One way to address the scalability issue is dividing systems into subsystems via a tree-like containment hierarchy. A somewhat more advanced approach is to provide ways to focus, in different diagrams, on different aspects of the interaction of a single component.)

• Applicability of the introduced notation for the design of interactions in complex control systems

Our approach is not to invent the wheel all over again. Instead, we want to build upon the existing body of knowledge provided by some existing formal method. We opt for CSP theory because of its wide acceptance, significant influence in the scientific world, solid body of knowledge and existence of the tools. Additional reason in favor of CSP is a lot of experience present in our lab in applying its occam implementation in the design of complex control systems.

The basic idea is to create the graphical representation of CSP and in that way bring the benefits obtained by relying on CSP closer to industrial practice. A graphical way of entering designs will allow engineers, ignorant to mathematics behind the CSP theory, to draw programs that are liable to formal verification based on CSP and the FDR tool (Formal Systems, 2005).

### 1.3.2 Local context

This research was carried out within a context defined by several preceding research projects.

During Hilderink's project (Hilderink, 2005a), basic concepts, and libraries were designed in order to bring occam-like concurrency in a modern software development practice. A first step was the implementation of libraries that provide occam-like compositional and synchronization primitives in popular programming languages (C++, Java, C) (Hilderink et al., 1997). Those libraries are known as CT libraries. A second step was the creation of a graphical modeling language (GML) (Hilderink, 2003) tailored for the design of occam-like CSP-based applications.

The next project (Jovanovic, 2006) in the line was oriented towards practical exploitation of the concepts through the implementation of a design tool (gCSP). gCSP tool (Jovanovic et al., 2004) is based on GML language and it is capable of generating source code for CT library, occam and machine readable CSP scripts. In addition, that project dealt with dependability issues in GML/CT based systems. The gCSP tool is capable to generate an FDR compatible CSP representation of the GML designs.

However, some important topics, like simulation of functional and extra-functional properties, real-time analysis, distributed communication, component-based development and many other topics were not researched in the scope of the aforementioned projects.

The initial aim of this project was to use the GML/CT approach in distributed realtime control systems with focus on the distribution aspects (e.g. designing the support for distribution in CT library and estimating the influence imposed by using fieldbus network interconnections inside control systems). During the work on various practical assignments, some advantages and disadvantages of GML/CT approach were identified. As a result, the decision was made to move the research topic towards improving the ways to specify concurrent systems in a graphical way. Chapter 2 provides background information that motivates this decision.

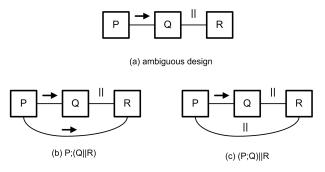

Briefly stated, GML is based on relating process blocks via binary relationships. This approach does offer significant design freedom, which is useful in early stages of the design process. However, using the approach based on binary relationships to specify control flow, makes the control flow difficult to grasp fast in complex GML based designs.